# Advanced Analog Building Blocks Transistor Level Logic

(comerma@physi.uni-heidelberg.de)

Course web

SoSe 2017

Introduction Other characteristics Combinational logic Sequential logic

## Standard cells

Digital logic are in fact analog circuits

Yes that's true!!

- Set of "basic blocks" grouped in Standard Cells.

- CMOS: Complementary metal-oxide-semiconductor, from complementary structures in logic.

- Standard Cells have several constrains/characteristics;

- Fixed height and variable width.

- Fixed position of VDD and GND.

- Set of important characteristics;

- Delay/speed.

- Power consumption.

- Driving power.

Introduction Other characteristics Combinational logic Sequential logic

- Rising/falling edge:

- Designed to have same rising and falling time at output!!

- Driving power:

- Is measured as integer values of how much simple inverters the cell can drive.

- Naming convention: INV1, INV2,... AND1,AND2,...

Introduction Other characteristics **Combinational logic** Sequential logic

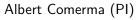

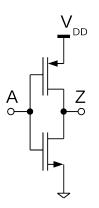

#### Combinational logic: Inverter

Simpler cell is an inverter (remember amplifiers?).

Standard cells Place and route Other characteristics Combinational logic Sequential logic

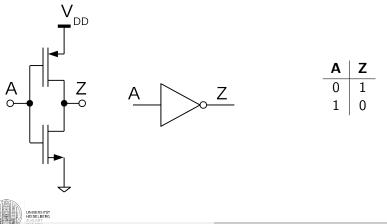

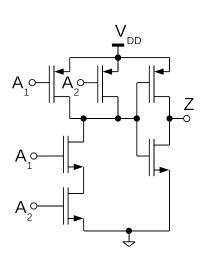

### Combinational logic: NAND gate

# NAND Gate:

Advances Analog Building Blocks: Transistor Level Logic 4 / 13

Introduction Other characteristics **Combinational logic** Sequential logic

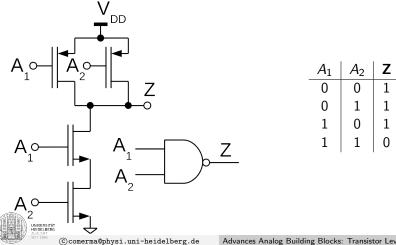

### Combinational logic: NOR gate

# NOR Gate:

©comerma@physi.uni-heidelberg.de Advances Analog Building Blocks: Transistor Level Logic 5 / 13

Standard cells Standard cells examples Place and route Standard cells examples Place and route Sequential logic

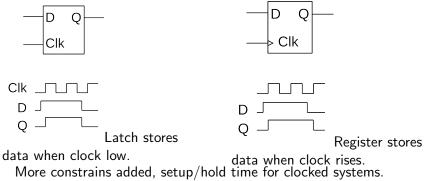

Of course sequential cells can also be used/implemented;

#### Inverter

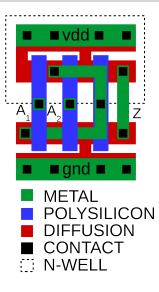

AND Gate Layout of Standard cells Layout of Standard cells II

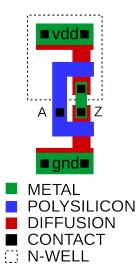

#### Standard cell example: Inverter

#### Inverter

AND Gate Layout of Standard cells Layout of Standard cells II

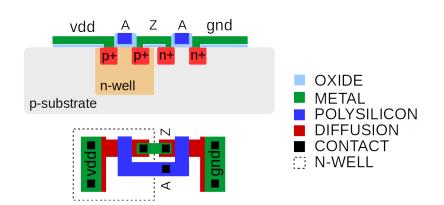

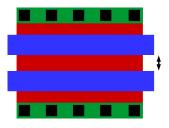

#### Inverter Cross section

Inverter AND Gate Layout of Standard cells Layout of Standard cells II

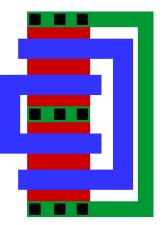

#### Standard cell example: AND gate

Inverter AND Gate Layout of Standard cells Layout of Standard cells II

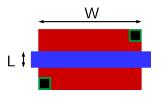

## Layout of Standard cells

- Transistors use minimum Length usually.

- Effective R scales linearly with 1/W.

- Gate capacitance scales linearly with W.

- Diffusion capacitance scales linearly with W.

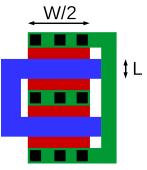

Some recommendation for long transistors:

• Long transistors have large

©comerma@physi.uni-heidelberg.de

• Folded reduces diffusion C,

Advances Analog Building Blocks: Transistor Level Logic 10 / 13

Inverter AND Gate Layout of Standard cells Layout of Standard cells II

#### Layout of Standard cells

Some recommendation for long transistors:

Series transisors as close as possible reduce R and C parasitics.

©comerma@physi.uni-heidelberg.de

• Folded stack not individual transistors.

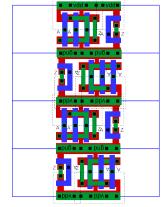

Place and route

• Digital tools start with defining a grid for placement;

- Cells are placed at each row with interleaved rotation.

- Metals are routed in horizontal and vertical directions.

#### Modern standard cells

- Modern technologies provide different "flavours" of standard cells.

- They can be combined by synthesis tools depending on constrains.

- Use of different types of transistors;

- Regular-Voltage-Threshold (STD)

- Used as default/reference.

- High-Voltage-Threshold (HVT)

- Slower.

- Less power consumption.

- Low-Voltage-Threshold (LVT)

- Faster.

- More power consumption.

Design an AND gate with following requirements;

- Same rising/falling time.

- Driving power = 1 (an inverter must be designed also).

- Minimum size as possible.

Are the rising/falling times equal in MonteCarlo? Can you fit it in  $3\mu m$  height?